## **Aphrodite**

Security

Properties of

RISC-V

Juni L DeYoung NWSA-AAASPD 2023 Meeting Western Washington University 22 March 2023

## Table of contents

#### **Overview**

Computer architecture, instruction sets, and emulation

#### **Emulating RISC-V**

Data generation is a complicated profession

#### **Aphrodite**

Design choices and the engineering process

# 1.1 Goals

What are we doing and why are we doing it?

What are securityrelevant properties

of computer

hardware?

### Research Process

#### Collect

#### Model processor in software

Record register transfers

#### **Analyze**

- 3. Mine traces for properties

- 4. Check properties against common weaknesses

#### Report

5. Security

properties found!

# 1.2 Background

What exactly are we studying here?

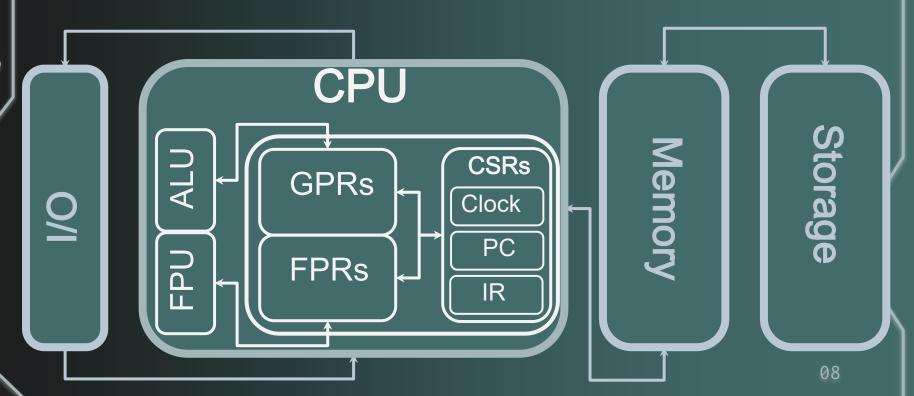

## **Computer Anatomy**

## Virtualizing Hardware

#### **Simulation**

- Recreates a processor at register

transfer level (RTL)

- Modeling the actual configuration of wires and transistors in software

#### **Emulation**

- Recreates an instruction-set

architecture (ISA)

- Doesn't replicate specific hardware idiosyncrasies, only its instruction set

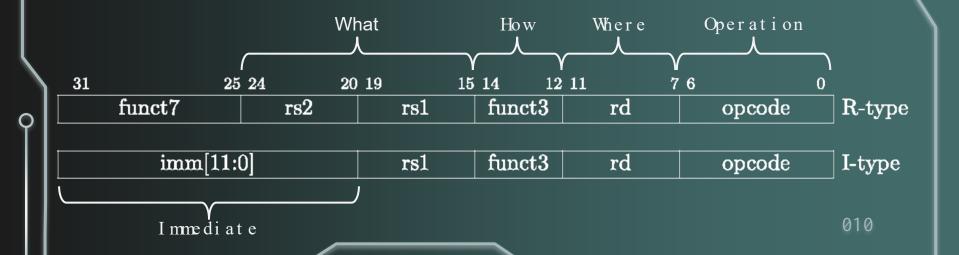

#### **Instructions**

- Contained in memory

- Addresses correspond to values in the program counter

- Control information flow through the processor

- Performing operations (arithmetic, load/store, navigation)

## **ISA Paradigms**

#### RISC

- One operation per instruction

- "Load-Store" architecture

- More difficult to write programs in assembly

- ARM

#### CISC

- "Microcoding"

- Instructions execute multiple operations at once

- Smaller programs

- Fewer main memory accesses

- x86

## Why Study RISC?

- CISC processors are proprietary trade secrets

- RISC architectures are easier to study

- Fixed-length instructions

- One instruction -> one operation

- RISC-V is an open-source design

- Funded by Intel and AMD

## The RISC-V Spec

- Highly customizable to different configurations

- Designed for academic study and hardware implementation

- 32- and 64-bit variants

#### General Purpose Registers x0-x31

- x0 is fixed to value 0

- x1-x31 are read as booleans or (un)signed 2's complement integers

#### Floating-point registers f0-f31

Correspond to IEEE standard for floating-point

#### Control and Status Registers

- 4096 CSRs, mostly used by the privileged architecture

- Some use in unprivileged code, mostly as counters and timers

- Exceptions, interrupts, traps, control transfer

## "Hello World"

```

.global start

Initialize the program at " start" label

start:

lui t0, 0x10000

Load address of serial port into register t0

andi t1, t1, 0

Zero out t1

addi t1, t1, 72

Add (int) 'H' = 72 to t1

sw t1, 0(t0)

Send value of t1 == 'H' to location addressed by t0 (UART0)

[\ldots]

The previous three lines are repeated for 'e', 'l', 'l', 'o'

and finally LF (line feed, aka '\n')

finish:

beq t1, t1, finish Jump to label finish if t1==t1

```

015

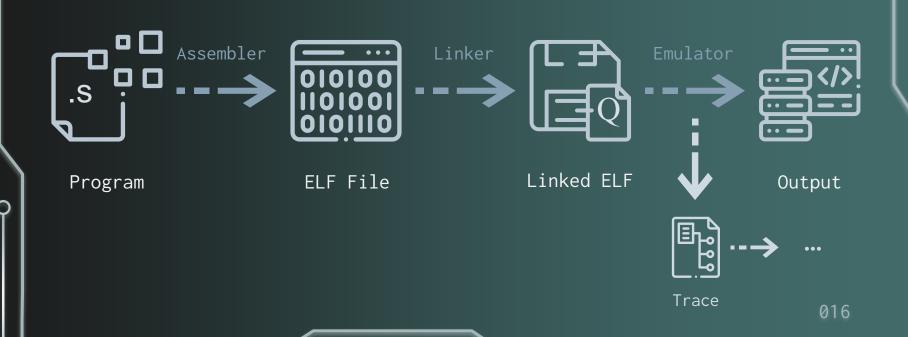

## Bare-Metal Programs on RISC-V

## **Data Mining**

.decls

make\_decls

017

## Aphrodite.py

QEMU

ELF

Register

Values

019

.dtrace

## Using QEMU in Aphrodite

```

args = [

"-machine", "virt", "-kernel", exe, "-

monitor", "stdio", "-S",

# options for running Fedora

"-smp", "4", "-m", "2G", "-bios",

"none",[...]

qemu = px.spawn("qemu-system-riscv64",

args, encoding="utf-8")

qemu.expect(".*(qemu)")

qemu.sendline("info registers")

qemu.expect("(qemu)")

qemu.sendline("c")

```

```

fedora-riscy login: root

Password:

Last failed login: Mon Jul 11 19:17:36 EDT 2022 on ttyS0

There were 3 failed login attempts since the last successful login.

[root@fedora-riscv ~]# ls

anaconda-ks.cfg

[root@fedora-riscv ~]# mkdir jldey

[root@fedora-riscv ~]# cd ildev

[root@fedora-riscv jldey]# ls

[root@fedora-riscv jldev]# echo "Hello World!"

Hello World!

[root@fedora-riscv jldey]# echo $PATH

/root/.local/bin:/root/bin:/usr/local/sbin:/usr/local/bin:/usr/sbin:

[root@fedora-riscv jldey]# echo $PATH > path.txt

[root@fedora-riscv jldev]# ls

path.txt

[root@fedora-riscv jldey]# cat path.txt

/root/.local/bin:/root/bin:/usr/local/sbin:/usr/local/bin:/usr/sbin:

```

Above: a sample session in the Fedora emulation

## Trace formats

#### <u>qtrace</u>

```

i\x1b[K\x1b[Din\x1b[K\[...]]

000000000001000\r

pc

mhartid 000000000000000\r

[\ldots]

x0/zero 00000000000000000

x1/ra 000000000000000000

x2/sp 00000000000000000

x3/gp 0000000000000000\r

[\ldots]

f28/ft8 00000000000000000

f29/ft9 00000000000000000

f30/ft10 00000000000000000

f31/ft11 00000000000000000\r

[\ldots]

```

#### <u>.dtrace</u>

```

..tick():::ENTER

this invocation nonce

pc

4096

mhartid

f31/ft11

```

## Parsing qtrace to dtrace

- 1. Create a .dtrace file and give it a unique name based on current system time

- 2. Spawn QEMU with initial parameters

- 3. While not timed out:

- a. Parse info registers output for register values, adding to list vals

- b. If vals is not equal to the last timepoint <u>and</u> is nonempty:

- i. Split vals entries into tuples: (label, value)

- ii. Cast the value hex string to an integer

- iii.Write these label/value pairs to .dtrace in the appropriate format

- c. Send next info registers command to QEMU

- 4. Quit QEMU and close .dtrace

## Parsing qtrace to dtrace

```

# find all register name/value pairs on current line

103

104

# returns empty list if no register values found,

# i.e. the output was not a string of register/value pairs

105

vals = re.findall(r"[a-z0-9/]+\s+[0-9a-f]{16}|\w+\s+[0-9a-f]x[0-9a-f]",out)

106

118

# Parse register/value pairs into lists

119

for reg in vals:

120

reg_val = re.split("\s+",reg)

# hex string to int: `int("ff",16)` -> 255

121

122

reg_val[1] = int(reg_val[1],16)

# register name\n value \n constant 1

123

124

dt.write(reg_val[0]+"\n"+str(reg_val[1])+"\n1\n")

# for copying these values into the tick exit

125

023

tpoint.append(reg_val)

126

```

## **Data Mining**

.decls

make\_decls

024

## **Properties**

```

f23/fs7 >= 0

f21/fs5 == f26/fs10

f24/fs8 one of { 0, 4607182418800017408L }

pc != 0

f25/fs9 one of { -4616189618054758400L, 0

mhartid == 0

mip >= 0

[\ldots]

mideleg one of { 0, 546 }

pc != mhartid

medeleg one of { 0, 45321 }

[\ldots]

mtvec one of { 0, 2147484904L }

mhartid <= mip</pre>

x0/zero == 0

[\ldots]

f0/ft0 >= 0

mip <= mie</pre>

[\ldots]

[\ldots]

f16/fa6 >= 0

mie <= mtvec</pre>

f19/fs3 one of { 0, 4607182418800017408L }

mideleg <= medeleg</pre>

f20/fs4 one of { -4616189618054758400L, 0

[\ldots]

mtvec >= mcause

f21/fs5 one of { 0, 4472406533629990549L }

f0/ft0 >= f20/fs4

025

f22/fs6 >= 0

[\ldots]

```

# Aphrodite verifies properties guaranteed by the ISA specification.

## Questions?

jldeyoung@willamette.edu

willamette.edu/~jldeyoung

github.com/wu-jldeyoung

CREDITS: This presentation template was created by **Slidesgo**, and includes icons by **Flaticon**, and infographics & images by **Freepik**

Please keep this slide for attribution